# ARM Processors ITMC301 L1 Introduction

#### By: Dr. Abdussalam Nuri Baryun

Mobile Computing Department, Faculty of Advance Technology, University of Tripoli

#### **Course Evaluation**

- 20% Quiz

- 30% mid-test

- 50% Final

- ARM documents (www.arm.com)

- A., Sloss, et al., ARM System Developer's Guide.

- Course handed sheets.

#### Used ARM processors

Automotive and ADAS Systems

By: Dr. Abdussalam Baryun

### Definitions

- Processor, and Microprocessor:

- Microcontroller:

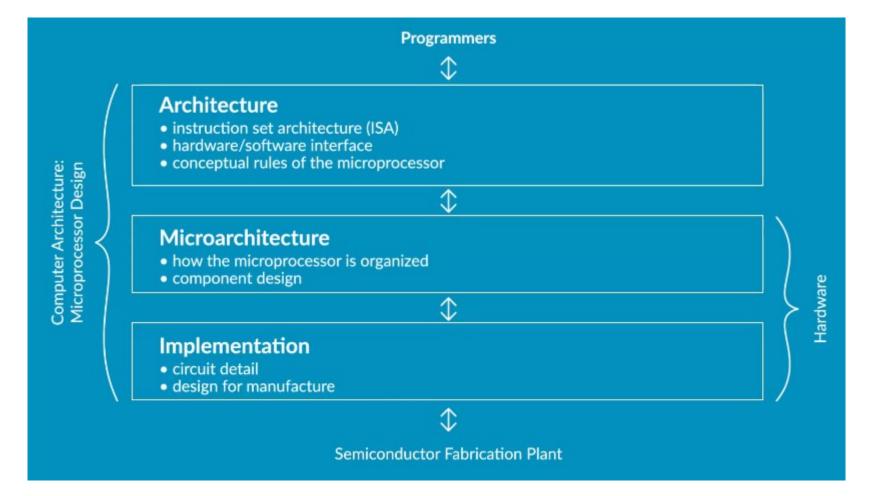

- Architecture, and Microarchitecture:

- Computer, and Microcomputer:

- Embedded System, SoC, and NoC

- MEMS

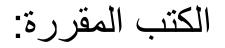

#### **Microprocessor Design Factors**

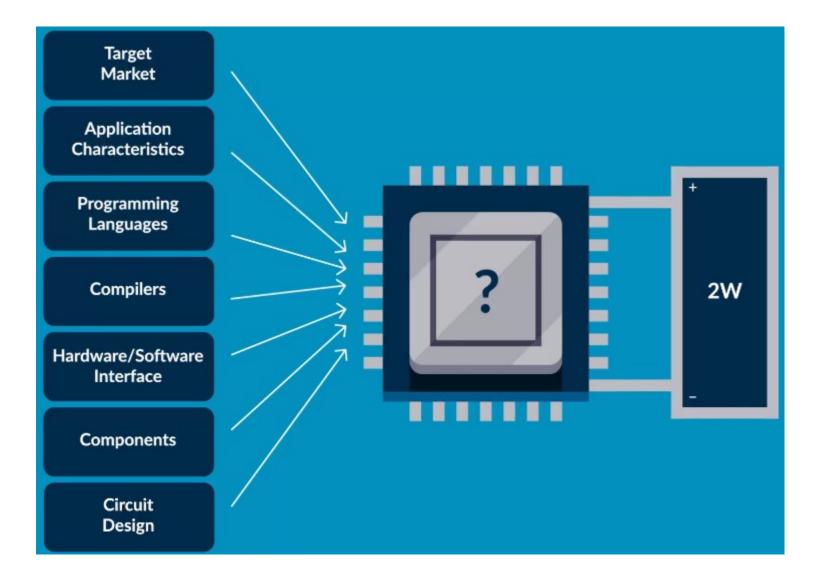

#### **Design Trade-offs**

#### Dr. Baryun

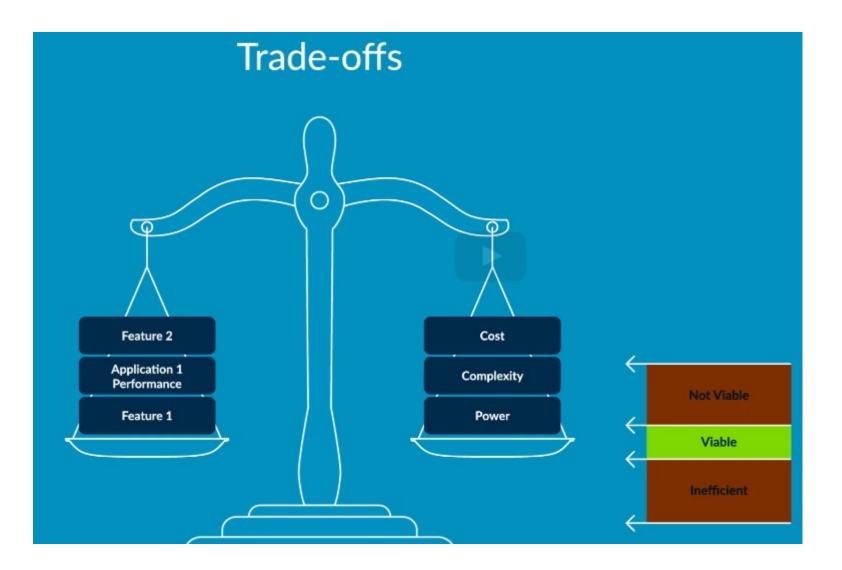

#### High demand Applications

#### Processor Resources

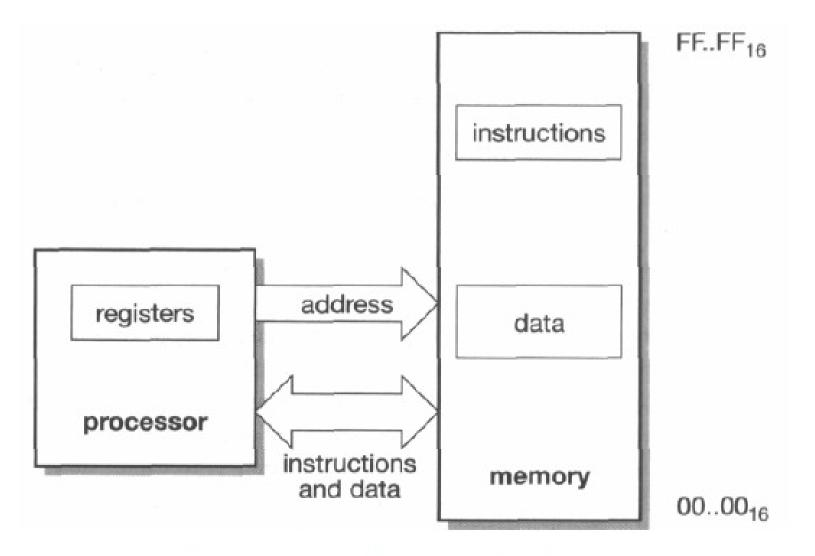

- A general-purpose processor is a finite-state automaton that executes instructions held in a memory. The state of the system is defined by the values held in the memory locations together with the values held in certain registers within the processor itself.

- Each instruction defines a particular way the total state should change and it also defines which instruction should be executed next.

## What processors do?

- It is a common misconception that computers spend their time computing, that is, carrying out arithmetic operations on user data.

- In practice they spend very little time 'computing' in this sense. Although they do a fair amount of arithmetic, most of this is with addresses in order to locate the relevant data items and program routines. Then, having found the user's data, most of the work is in moving it around rather than processing it in any transformational sense.

### What processors spend time on?

Typical dynamic instruction usage.

| Instruction type      | Dynamic usage |

|-----------------------|---------------|

| Data movement         | 43%           |

| Control flow          | 23%           |

| Arithmetic operations | 15%           |

| Comparisons           | 13%           |

| Logical operations    | 5%            |

| Other                 | 1%            |

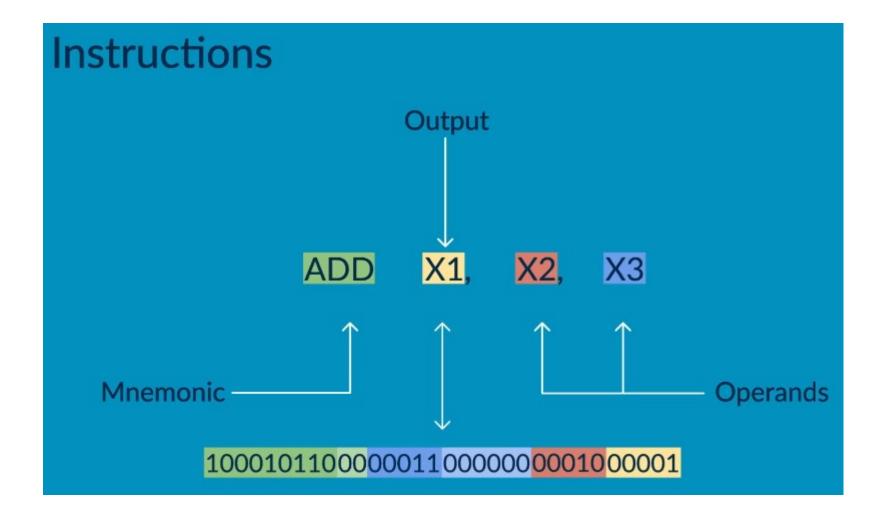

### Instruction Set Architecture (ISA)

- ISAs are related to microprocessor

- Instruction Types

- Arithmetic

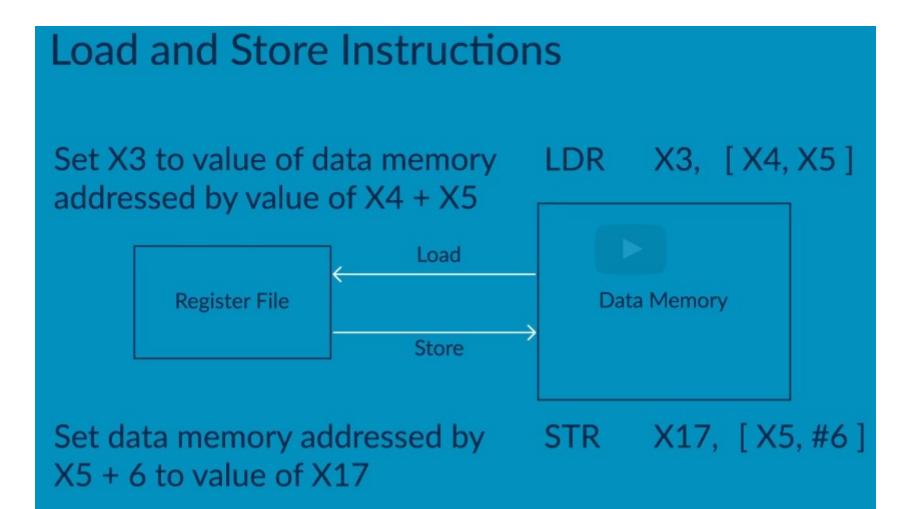

- Load and Store

- Branch

#### How Do You Tell a Microprocessor What to Do

The state in a stored-program digital computer.

By: Dr. Abdussalam Baryun

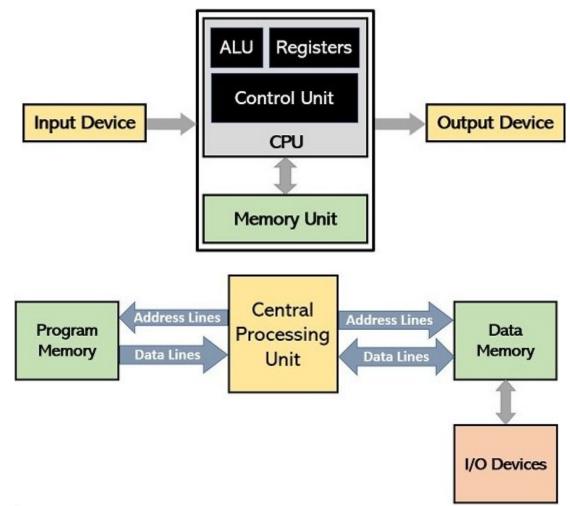

#### **Two Principle Processing Architectures**

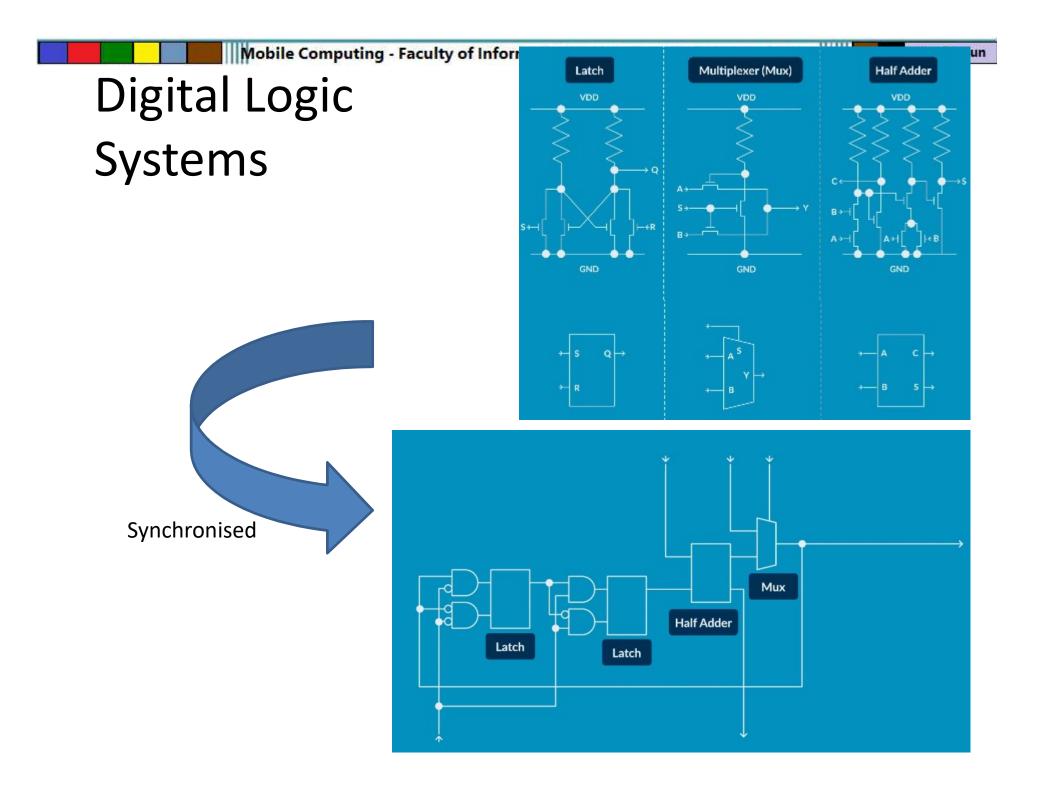

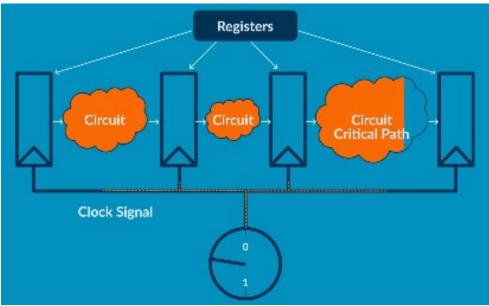

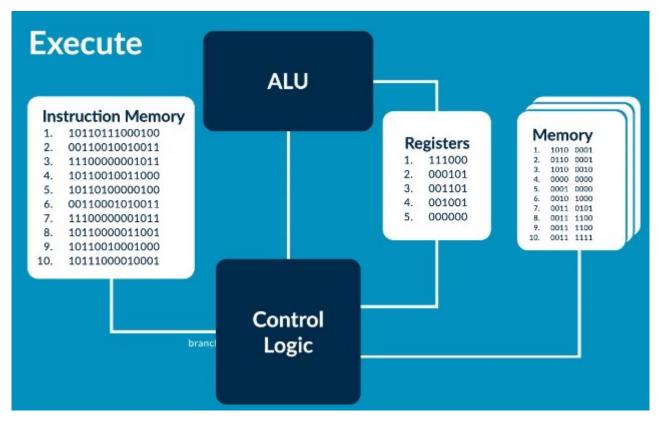

# When designing a digital system

We must keep everything synchronized to control behavior.

- To do this, we use a "Clock Signal," which is a wire in the circuit whose signal cycles between zero and one. We measure the rate in Hertz.

- For example, if you hear a processor has a clock speed of two Gigahertz, it means 2 billion ones and zeroes per second.

- The maximum speed of the clock signal is determined by the longest, and therefore slowest, path in the circuit between 2 clocked flip-flops.

- This is referred to as the "Critical Path." The signal must have time to propagate all the way along the critical path before the clock cycle completes.

## Critical path

The maximum speed of the clock signal is determined by the longest, and therefore slowest, path in the circuit between 2 clocked flip-flops

#### Processing needs Memory

- In addition to logic, a microprocessor needs memory.

- Memory is organized as arrays of memory cells that are able to store many "Words" of data.

- A specific word, commonly 32 bits in length, can be accessed by specifying its "Address."

- Each address is a number that indicates the location in the memory that should be read or written.

- Memory cells range from hundreds of bits to millions of bits in size, but larger ones are slower to access, as signals and their long internal wires take longer to propagate.

- For that reason, almost all microprocessors include at least two types for storing data: a big slow "Data Memory," and a small fast memory called a "Register File."

- In reality, the "Data Memory" may be implemented using many different sizes of memory, as well as storing data in memory, we also use some memory to store the instructions.

- We need a way to keep track of which instruction we will fetch next, so we have a "Program Counter."

|                              | Address |          | Wo       | ords     |          |   |

|------------------------------|---------|----------|----------|----------|----------|---|

| [                            | 0:      | 00011000 | 11110111 | 10000000 | 01001011 |   |

|                              | 1:      | 10101011 | 01001010 | 10010000 | 11111011 |   |

|                              | 2:      | 11010101 | 01010101 | 10001100 | 01000000 |   |

| Address                      | 3:      | 10101110 | 11111111 | 10000000 | 00000000 |   |

| $13 \rightarrow \rightarrow$ | 4:      | 00011000 | 00000000 | 10000100 | 00001001 |   |

|                              | 5:      | 11010101 | 00000000 | 10111000 | 01111011 |   |

| D                            | 6:      | 00000000 | 0000001  | 10000000 | 10000000 |   |

| Read/Write?                  | 7:      | 00010000 | 00000011 | 10001100 | 11111011 | V |

| lead $\longrightarrow$       | 8:      | 00000000 | 11110000 | 10000000 | 00000001 |   |

|                              | 9:      | 00011001 | 00110101 | 10010110 | 10000000 |   |

| Value                        | 10:     | 01111000 | 11000111 | 10100011 | 00000000 |   |

| Value                        | 11:     | 00010110 |          | 10000100 | 00000000 |   |

| · · · · ·                    | 12:     | 00011000 | 11000001 | 10111000 |          |   |

|                              | 13:     | 00011001 | 00110101 | 10010110 | 10000000 |   |

|                              | 14:     | 00011111 | 11111111 | 10000000 | 11100101 |   |

|                              | 15:     | 00011000 | 00000000 | 11100000 | 01111000 |   |

|                              | 16:     | 00011110 | 10010101 | 00000000 |          |   |

| Memory                       | 17:     | 00011001 | 10000001 | 11111000 | 01001011 |   |

#### Read

|             | Address           |                                  | Wo                               | ords                             |                                  |                |

|-------------|-------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------|

|             | 0:<br>1:<br>2:    | 00011000<br>10101011<br>11010101 | 11110111<br>01001010<br>01010101 | 10000000<br>10010000<br>10001100 | 01001011<br>11111011<br>01000000 | 1000000        |

| Address     | 3:<br>4:          | 10101110<br>00011000             | 11111111<br>00000000             | 10000000<br>10000100             | 00000000<br>00001001             |                |

| Read/Write? | 5:<br>6:<br>7:    | 11010101<br>00000000<br>00010000 | 00000000<br>00000001<br>00000011 | 10111000<br>10000000<br>10001100 | 01111011<br>10000000<br>11111011 | Value 70010110 |

| >           | 8:<br>9:<br>10:   | 00000000<br>00000000<br>01111000 | 11110000<br>00000111<br>11000111 | 10000000<br>10111110<br>10100011 | 00000001<br>11000001<br>00000000 |                |

| Value       | 11:<br>12:        | 00010110<br>00011000             | 10000000<br>11000001             | 10000100<br>10111000             | 00000000<br>00000000             | 00110101       |

|             | 13:<br>14:<br>15: | 00011001<br>00011111<br>00011000 | 00110101<br>1111111<br>00000000  | 10010110<br>10000000<br>11100000 | 10000000<br>11100101<br>01111000 |                |

| Memory      | 16:<br>17:        | 00011110<br>00011001             | 10010101<br>10000001             | 00000000<br>11111000             | 01011111<br>01001011             | 00011001       |

- larger memory ones are slower to access,

- as signals and their long internal wires take longer to propagate.

- For that reason, almost all microprocessors include at least two types for storing data:

- a big slow "Data Memory," and a small fast memory called a "Register File."

- In reality, the "Data Memory" may be implemented using many different sizes of memory,

#### Write

|                                     | Address |               | Words |          |          |          |          |       |

|-------------------------------------|---------|---------------|-------|----------|----------|----------|----------|-------|

|                                     |         |               | 0:    |          |          | 10000000 |          |       |

|                                     |         |               | 1:    |          | 01001010 | 10010000 |          |       |

| - Andreas                           |         |               | 2:    | 11010101 | 01010101 |          | 01000000 |       |

| Address                             |         |               | 3:    |          | 11111111 |          | 00000000 |       |

| →                                   | _       |               | 4:    | 00011000 | 00000000 | 10000100 |          |       |

|                                     |         |               | 5:    |          | 00000000 | 10111000 |          |       |

| Devel (MARSH-2)                     |         |               | 6:    | 00000000 | 00000001 | 10000000 | 10000000 | Malar |

| Read/Write?                         |         |               | 7:    | 00010000 | 00000011 | 10001100 | 11111011 | Value |

|                                     |         |               | _     | 00000000 | 11110000 | 10000000 | 0000001  |       |

|                                     |         | $\rightarrow$ | 9:    | 00000000 | 00000111 | 10111110 | 11000001 |       |

| Malua                               |         | 1             | 0:    | 01111000 | 11000111 |          | 00000000 |       |

| Value                               |         | 1             | 1:    | 00010110 | 10000000 | 10000100 | 00000000 |       |

| 00011001 00110501 10050110 10000000 |         | 1             | 2:    | 00011000 | 11000001 | 10111000 | 00000000 |       |

|                                     |         | 1             | 3:    | 00011001 | 00110101 | 10010110 | 10000000 |       |

|                                     |         | 1             | 4:    | 00011111 | 11111111 | 10000000 | 11100101 |       |

|                                     |         | 1             | 5:    | 00011000 | 00000000 | 11100000 | 01111000 |       |

|                                     |         | 1             | 6:    | 00011110 | 10010101 | 00000000 | 01011111 |       |

| Memory                              |         | 1             | 7:    | 00011001 | 10000001 | 11111000 | 01001011 |       |

#### Computing Memory

We need Register File, Data Memory, Instruction Memory. •

| 0: 00011000 11110111 10000000 01001011  | 12        |                                                                                    |                                                                                    |

|-----------------------------------------|-----------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| 1: 10101011 01001010 10010000 11111011  |           | 0: 00011000 11110111 10000000 01001011                                             | 34: 00011000 11110111 10000000 01001011                                            |

| 2: 11010101 01010101 10001100 01000000  |           | 1: 10101011 01001010 10010000 11111011                                             | 35: 10101011 01001010 10010000 11111011                                            |

| 3: 10101110 11111111 10000000 00000000  |           | 2: 11010101 01010101 10001100 01000000                                             | 36: 11010101 01010101 10001100 01000000                                            |

| 4: 00011000 00000000 10000100 00001001  |           | 3: 10101110 11111111 10000000 00000000                                             | 37: 10101110 11111111 10000000 00000000                                            |

| 5: 11010101 00000000 10111000 01111011  |           | 4: 00011000 00000000 10000100 00001001                                             | 38: 00011000 00000000 10000100 00001001                                            |

| 6: 00000000 00000001 10000000 10000000  |           | 5: 11010101 00000000 10111000 01111011                                             | 39: 11010101 00000000 10111000 01111011                                            |

| 7: 00010000 00000011 10001100 11111011  |           | 6: 00000000 00000001 10000000 10000000                                             | 40: 00000000 00000001 10000000 10000000                                            |

| 8: 00000000 11110000 10000000 00000001  |           | 7: 00010000 00000011 10001100 11111011                                             | 41: 00010000 00000011 10001100 11111011                                            |

| 9: 00000000 00000111 10111110 11000001  |           | 8: 00000000 11110000 10000000 00000001                                             | 42: 00000000 11110000 10000000 00000001                                            |

| 10: 01111000 11000111 10100011 00000000 |           | 9: 00000000 00000111 10111110 11000001                                             | 43: 00000000 00000111 10111110 11000001                                            |

| 11: 00010110 10000000 10000100 00000000 |           | 10: 01111000 11000111 10100011 00000000                                            | 44: 01111000 11000111 10100011 00000000                                            |

| 12: 00011000 11000001 10111000 00000000 |           | 11: 00010110 10000000 10000100 00000000                                            | 45: 00010110 10000000 10000100 00000000                                            |

| 13: 00011001 00110101 10010110 10000000 | →         | 12: 00011000 11000001 10111000 00000000                                            | 46: 00011000 11000001 10111000 00000000                                            |

| 14: 00011111 11111111 10000000 11100101 |           | 13: 00011001 00110101 10010110 10000000                                            | 47: 00011001 00110101 10010110 10000000                                            |

| 15: 00011000 00000000 11100000 01111000 |           | 14: 00011111 11111111 10000000 11100101                                            | 48: 00011111 11111111 10000000 11100101                                            |

| 16: 00011110 10010101 00000000 01011111 |           | 15: 00011000 00000000 11100000 01111000                                            | 49: 00011000 00000000 11100000 01111000                                            |

| 17: 00011001 10000001 11111000 01001011 |           | 16: 00011110 10010101 00000000 01011111                                            | 50: 00011110 10010101 00000000 01011111                                            |

|                                         | J →       |                                                                                    |                                                                                    |

|                                         |           | 17: 00011001 10000001 11111000 01001011                                            | 51: 00011001 10000001 11111000 01001011                                            |

| Register File                           |           | 18: 00011000 11110111 10000000 01001011                                            | 52: 00011000 11110111 10000000 01001011                                            |

|                                         |           | 19: 10101011 01001010 10010000 11111011                                            | 53: 10101011 01001010 10010000 11111011                                            |

| small and fast                          |           | 20: 11010101 01010101 10001100 01000000                                            | 54: 11010101 01010101 10001100 01000000                                            |

|                                         | · · · · · | 21: 10101110 11111111 10000000 00000000                                            | 55: 10101110 11111111 10000000 00000000                                            |

|                                         |           | 22: 00011000 00000000 10000100 00001001                                            | 56: 00011000 0000000 10000100 00001001                                             |

|                                         |           | 23: 11010101 00000000 10111000 01111011                                            | 57: 11010101 00000000 10111000 01111011                                            |

|                                         |           | 24: 0000000 0000001 10000000 10000000                                              | 58: 00000000 0000001 10000000 10000000                                             |

|                                         |           | 25: 00010000 00000011 10001100 11111011<br>26: 00000000 11110000 10000000 00000001 | 59: 00010000 00000011 10001100 11111011<br>60: 00000000 11110000 10000000 00000001 |

|                                         |           | 26: 0000000 00000111 1010000 0000001                                               | 61: 00000000 00000111 10111110 11000001                                            |

|                                         |           | 28: 01111000 11000111 10100011 00000000                                            | 62: 01111000 11000111 10100011 00000000                                            |

|                                         |           | 29: 00010110 10000000 10000100 00000000                                            | 63: 00010110 10000000 10000100 00000000                                            |

|                                         |           | 30: 00011000 11000001 10111000 00000000                                            | 64: 00011000 11000001 10111000 00000000                                            |

|                                         |           | 31: 00011001 00110101 10010110 10000000                                            | 65: 00011001 00110101 10010110 10000000                                            |

|                                         |           | 32: 00011111 11111111 10000000 11100101                                            | 66: 00011111 1111111 10000000 11100101                                             |

|                                         |           | 33: 00011000 00000000 11100000 01111000                                            | 67: 00011000 00000000 11100000 01111000                                            |

|                                         |           |                                                                                    |                                                                                    |

|                                         |           |                                                                                    |                                                                                    |

|                                         |           |                                                                                    |                                                                                    |

#### Data Memory larger and slower

#### Memory

### Program Counter (PC)

A Register to keep track of which instruction to be fetched next in process, it stores the memory address of the next instruction to be accessed

|              | 0: 00011000 11110111 10000000 01001011 34: 00011000 11110111 10000000 01001011<br>1: 10101011 01001010 10010000 11111011 35: 10101011 01001010 10010000 11111011                                                                                                                                                                                                                                                                                                                  | Instruction<br>Decode Logic |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

|              | 2:   11010101   01010101   10001100   01000000     3:   10101110   1111111   10000000   36:   10101010   110001100   01000000     4:   00011000   000000000   10001000   00000000   37:   1010110   1111111   10000000   00000000     5:   11010101   00000000   10001000   00001000   38:   00011000   00000000   00000000     5:   11010101   000000000   10111000   01111011   39:   11010101   00000000   01111011                                                            |                             |

| Program      | 6:   00000000   00000001   10000000   40:   00000000   00000001   10000000     7:   00010000   000000011   10001100   1111011   41:   00010000   0001100   1111011     8:   00000000   01100001   00000001   42:   00000000   10000000   00000001     9:   00000000   00000111   1011110   10000001   43:   00000000   00000001                                                                                                                                                   |                             |

| Counter (PC) | 10:   01111000   11000111   10100011   0000000   44:   01111000   11000111   1010011   0000000     11:   0001010   1000000   10000100   0000000   45:   0001010   10000100   0000000     12:   0001100   1000001   1011100   0000000   46:   0001100   1011000   0000000     13:   00011001   0010101   1000000   47:   00011001   10010110   1000000                                                                                                                             |                             |

| 36 →         | 14: 00011111 11111111 10000000 11100101 48: 00011111 11111111 10000000 11100101   15: 00011000 00000000 11100000 01111000 49: 0001100 00000000 01111000   16: 00011110 10010101 00000000 01011111 50: 00011110 10000000 01011111   17: 00011001 100000001 11111000 01001011 51: 00011001 100000001 11111000 01001011                                                                                                                                                              |                             |

|              | 17:   00011001   10000001   1111000   01001011   51:   00011001   1111000   01001011     18:   00011000   11110111   10000000   01001011   52:   00011000   11110111   10000000   01001011     19:   10101011   01010010   10010000   1111011   53:   10101010   10010000   1111011     20:   11010101   01010101   10000100   01000000   54:   11010101   10001100   01000000     21:   1010110   11111111   10000000   00000000   54:   1010110   1111111   10000000   00000000 |                             |

|              | 22:   00011000   0000000   10000100   00001001   55:   00011000   0000000   10000001     23:   11010101   00000000   10111000   01111011   57:   11010101   00000000   10111001     24:   00000000   00000000   10111000   01111011   57:   11010101   00000000   10111010     24:   00000000   00000000   10000000   10000000   58:   00000000   10000000   10000000     25:   00010000   0000011   10001100   1111111   57:   00010000   00000001   10000000                    |                             |

|              | 26:   00000000   11110000   10000000   00000001   50:   00000000   11110000   10000000   00000001     27:   00000000   00000111   1011110   11000001   61:   00000000   00000000     28:   01111000   11000011   00000000   62:   01111000   11000011   00000000     29:   0001010   10000000   00000000   63:   00010110   10000000   00000000                                                                                                                                   |                             |

|              | 30:   00011000   11000001   10111000   00000000   64:   00011000   10111000   00000000     31:   00011001   00110101   10010100   10000000   65:   00011001   00101010   10000000     32:   00011111   11111111   10000000   11100101   66:   00011111   1111111   10000000   11100101                                                                                                                                                                                            | 8                           |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                             |

#### Instruction Memory

Most modern machines are byte-addressable (8-bit)

If you have more specialized hardware, (embedded microcontrollers, etc) that are word addressable (16-bit, 32-bit), then you are correct that you would multiply

```

memory locations possible 2<sup>n</sup> * (word-size in bits) / (8) = # of bytes.

```

Normally, a processor with a 32-bit architecture can only address 4 GiB of physical memory at any given time (2<sup>32</sup> = 4294967296). Each byte of physical memory has its own address.

To determine the ammount of memory that can be addressed we need to know three things.

- The size of the smallest addressable unit of memory. On pretty much all current general purpose computers this is the 8-bit byte. Computers do not generally address memory in bits.

- The usable size the physical address. This may be the same as the data word size of the processor but it often isn't.

- Whether any memory address ranges need to be used for things other than memory. Most systems place IO devices in the memory map reducing the ammount of space available for regular memory (sometimes significantly so).

### What Are the Basic Components of a Microprocessor

#### Dr. Baryun

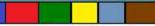

#### What Is the Fetch-Execute Cycle

#### Fetch – Decode - Execute •

### Pipelining

#### Simple Processor

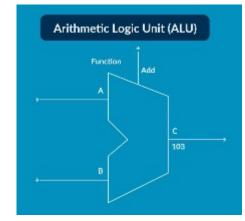

A simple form of processor can be built from a few basic components:

- A program counter (PC) register that is used to hold the address of the current instruction; a single register called an accumulator (ACC) that holds a data value while it is worked upon;

- An arithmetic-logic unit (ALU) that can perform a number of operations on binary operands, such as add, subtract, increment, and so on;

- An instruction register (IR) that holds the current instruction while it is executed;

- **Control Logic Unite (CLU)**: instruction decode and control logic that employs the above components to achieve the desired results from each instruction.

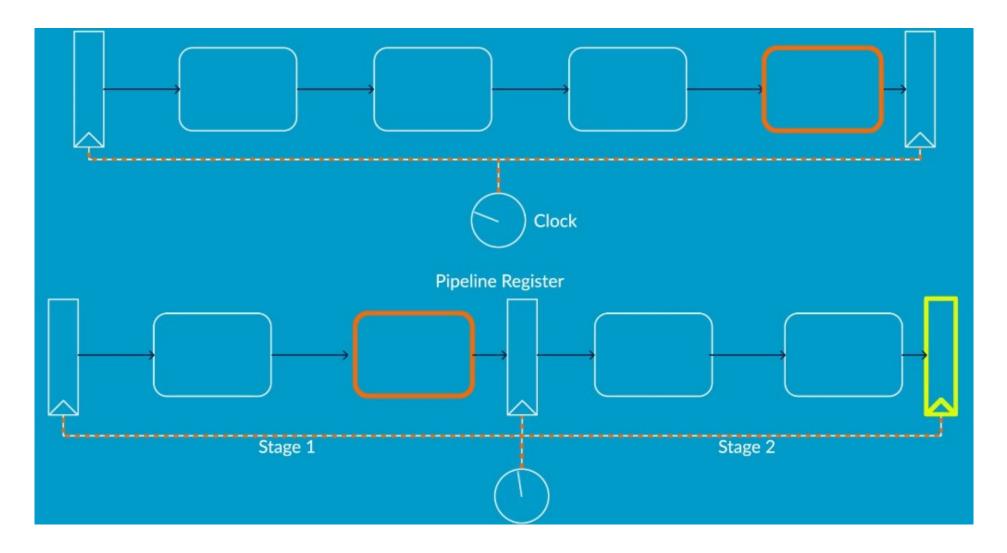

- Reduced Instruction Set Computer (RISC)

- Complex Instruction Set Computer (CISC)

- RISC is a design philosophy aimed at delivering simple but powerful instructions that execute within a single cycle at a high clock speed.

- Reducing the complexity of instructions performed by the hardware because it is easier to provide greater flexibility and intelligence in software.

- A RISC design places greater demands on the compiler.

CISC vs. RISC. CISC emphasizes hardware complexity. RISC emphasizes compiler complexity.

| CISC                                       | RISC                                               |

|--------------------------------------------|----------------------------------------------------|

| Many instructions                          | Few instructions                                   |

| Instructions have varying lengths          | Instructions have fixed lengths                    |

| Instructions execute in varying times      | Instructions execute in 1 or 2 bus cycles          |

| Many instructions can access memory        | Few instructions can access memory                 |

|                                            | • Load from memory to a register                   |

|                                            | • Store from register to memory                    |

| In one instruction, the processor can both | No one instruction can both read and write         |

| • read memory and                          | memory in the same instruction                     |

| • write memory                             |                                                    |

| Fewer and more specialized registers.      | Many identical general purpose registers           |

| • some registers contain data,             |                                                    |

| • others contain addresses                 |                                                    |

| Many different types of addressing modes   | Limited number of addressing modes                 |

|                                            | • register,                                        |

|                                            | • immediate, and                                   |

|                                            | • indexed.                                         |

| • others contain addresses                 | <ul><li>register,</li><li>immediate, and</li></ul> |

#### What is ARM

- Acorn RISC Machine

- Advanced RISC Machines (ARM)

- The important concept of the *Reduced Instruction Set Computer (RISC)*

- System-on-Chip (SoC)

- The ARM core uses a RISC architecture.

- The ARM architecture incorporated a number of features from the Berkeley RISC design, but a number of other features were rejected. Those that were used were:

- a load-store architecture;

- fixed-length 32-bit instructions;

- 3-address instruction formats.

#### **RISC** Features rejected

The RISC features that were rejected by the ARM designers were:

- Register windows.

- Delayed branches.

- Single-cycle execution of all instructions.

## ARM development

- The highlights of the last decade of ARM development include:

- The introduction of the novel compressed instruction format called 'Thumb' which reduces cost and power dissipation in small systems;

- Significant steps upwards in performance with the ARM9, ARM 10 and 'Strong- ARM' processor families;

- A state-of-the-art software development and debugging environment;

- A very wide range of embedded applications based around ARM processor cores.

### **The Reference:**

# [1] A., Sloss, et al., ARM System Developer's Guide.